2026-05-03 22:00:15

There are plenty of photos of the International Space Station out there on the Internet, but taking your own from ground level is a special challenge. [saveitforparts] recently decided to attempt this feat using a $15 thrift store lens.

The cool thing about the digital photography revolution is that there is a lot of old film gear that can be had for cheap. In this case, [saveitforparts] found a 400mm Sigma XQ lens with a 2x teleconverter for just $14.99. Paired with an adapter, it sat nicely on a Sony NEX-3 digital camera, ready to try and capture the ISS as it passed overhead. As you might imagine, aiming at the space station is not a point-and-shoot job. N2YO.com was used to figure out the best time to try and capture it. [saveitforparts] was able to capture the ISS as a white dot as it passed over, but couldn’t quite get enough zoom to really see the ISS in detail. [saveitforparts] was also able to repeat the feat with a Canon camcorder, too, but the image was still pretty blobby and didn’t show much. Later attempts involved capturing transits as the ISS passed by the Sun, though the ISS mostly appeared as a small speck.

[saveitforparts] did technically capture the ISS, just not closely enough to see much beyond a dot. It’s not the first time we’ve seen this attempted, though! If you try and capture the ISS with something truly ridiculous, like a Game Boy Camera or Kodak Charmera, you are honour-bound to tell us on the tipsline. Video after the break.

2026-05-03 19:00:22

Peristaltic pumps are a very simple and effect device for transferring fluids without said fluid ever coming into contact with any part of the pump mechanism. At their core they involve a mechanism squeezing fluids through compressible tubing, but there are various implementations of such a mechanism that all have their pros and cons. In a recent article by [T. K. Hareendran] over at EDN these types are discussed and when you’d want to pick one over the other.

Also known as a roller pump, these positive displacement pumps have been known since the 19th century, finding uses in industrial, medical, research, agriculture and many other fields. Each of these fields have different requirements with the use of a peristaltic pump as a dosing pump being a specific application whereby e.g. a stepper motor can be used to provide exact dosing.

For industrial settings the typical rollers that compress the tube are replaced with shoes that provide higher pressures and endurance, with overall a bewildering number of motor types and tubing materials available. Depending on what your project needs, you may opt for continuous flow, fine control over dosing, the ability to reverse the flow, etc.

Unless your project is particularly rugged, a roller-based mechanism should be fine, while silicone tubing is great for biocompatibility and PVC is a cheaper tube material option. If you intend to transfer certain kinds of chemicals that will react with each of these there are some more exotic tubing options available as well.

We have previously covered projects that use a peristaltic pump for rather interesting things, such as DIY pharmaceutics, in a home-grown flow battery, not to mention creating DIY peristaltic pumps from first principles.

2026-05-03 16:00:21

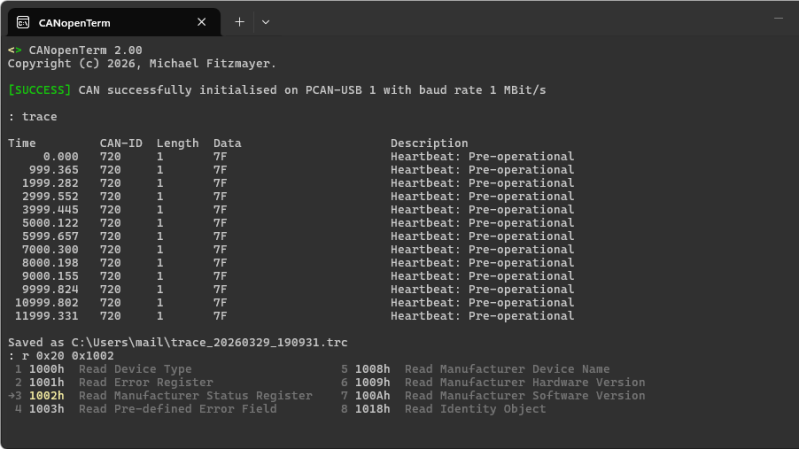

If you find yourself working with CANopen CC networks, you might find yourself in need of a tool for monitoring what’s happening on the wire. [Michael Fitzmayer] whipped up a piece of software to fulfil just that role.

CANopenTerm might be named after the CANopen standard, but it’s really a terminal-driven tool for working with CAN buses in general. The software is built for real-time use, allowing sniffing raw frames on the wire, tracing, and probing of nodes, all from within the console. It’s also possible to add scripting via Lua or Python for more advanced work, as well as do protocol-aware inspection if that’s relevant to your use case. The key idea of the software is to be fast and scriptable to suit a given need, rather than bogging everything down with a heavy GUI interface that’s slower to work with.

If you aren’t afraid of getting into the nitty gritty with CAN and like lightweight text-based interfaces, this might be the tool for you. We’ve also explored some other CAN visualization tools lately, as well. Ultimately, there is a lot of machinery out there running on some variant of CAN or other, so it pays to know how to work with it. If you’ve got your own projects cooking up in this space, don’t hesitate to let us know on the tipsline!

2026-05-03 13:00:31

C-3PO is one of the more famous movie robots out there. However, we don’t see a lot of replicas built, perhaps because in speech and mannerisms, he’s quite hard to replicate. Of course, that feat has become much more achievable with modern AI tech, as [Samuel Potozkin] demonstrates.

We’re not looking at a full C-3PO build here, it’s just the head—but for the project’s purposes, that’s all that was really required. The build relies on a Raspberry Pi 5 as the brains of the droid. It’s running a mic hooked up to a real time speech to text engine, and that text is then sent to a large language model for interpretation. Responses are then generated, passed through a processing layer to capture C-3PO’s general tone and vibe, and then handed off to a text-to-speech synth to imitate the iconic voice, played via speaker. The end result is a C-3PO you can actually talk to, which is something that might have knocked a few socks off when the movie first launched in 1977. In-depth materials for the build can be had via Google Drive and on Github.

This ersatz C-3PO isn’t an exact dupe of the movie ‘bot. The protocol droid is a little slow to respond, and the patter isn’t quite on point, even if the voice synth makes a good effort at mimicking the original. Overall, it’s a little… robotic… something you wouldn’t say of the character in the movies. Still, it’s a great effort, and something we haven’t really seen much of before. If you like more classic droid replicas, though, we’ve featured those too. Video after the break.

2026-05-03 10:00:08

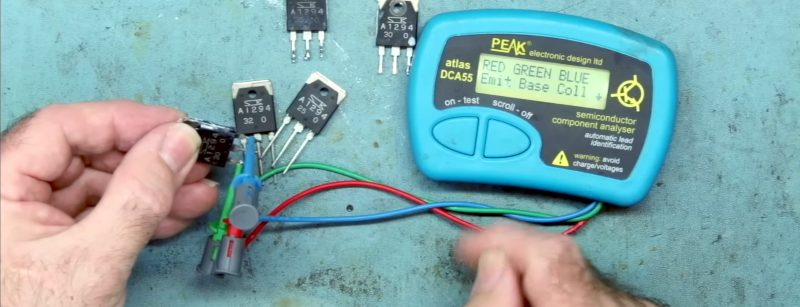

Transistors in some circuit configurations work together and, frequently, need to be matched. This is so common that you can sometimes find ICs that are just a pair of transistors made with the same piece of silicon, so they should be matched very closely by default. But with discrete transistors, two devices of the same type are not always identical. [Learn Electronics Repair] covers the topic and explains how to match devices in the video below.

Depending on the circuit, the matching parameters may be different, but generally, the idea is that you want similar gains or matching saturation characteristics. The reason is that when you have multiple transistors working together, you don’t want one to do more work than the other device. This is inefficient and could drive the “better” component to fail.

The same idea applies in bridge circuits, where you might match resistors or capacitors to make sure that, for example, two 10% resistors are very close to the same value. A 10K resistor could be between 9K and 11K, and you might not care as long as they are both, say, 9.2K or both 10.8K.

This is different, by the way, from impedance matching, where you achieve maximum power transfer by matching a source to a load.

2026-05-03 07:00:15

Once upon a time, someone set up a livestream wherein the messages from Twitch chat could control a game of Pokemon. Since then, we’ve seen Twitch control all sorts of things. If you’d like to have them play with some LEDs in your house, you might like this project from [pfeiffer3000].

The concept is simple enough. The heart of the build is an ESP32 microcontroller, which is easy to integrate with web services thanks to its onboard WiFi capability. It’s hooked upt o a string of WS2812B addressable RGB LEDs. The LEDs themselves are installed within table tennis balls to act as nice, spherical diffusers, and installed in a square frame made of PVC pipes. As for code, the rig uses the WLED library to drive the LED strings, and code from TwitchIO to interface with Twitch chat itself. It’s as simple as rigging up a bit of Python. With everything assembled, [pfeiffer3000] had an attractive LED grid that could be controlled directly by anyone watching their Twitch stream.

We’ve explored how to control things via Twitch before, too. It’s a fun way to add some interactivity to your livestream that really gets viewers involved. If you’ve been building your own audience-controlled projects, we’d love to hear about them on the tipsline!